在数字世界,用户存储在SSD上的数据最终会被保存至非易失性存储介质,而存储介质的特性直接影响SSD的主控和固件设计。NAND Flash是当前电子设备中常见的非易失性存储介质。在上一篇文章中,我们介绍了NAND Flash技术的演进历程和未来探索方向(点击查看),本篇文章将继续为大家讲解NAND Flash的基本原理和特性。

1、NAND Flash存储单元及操作原理

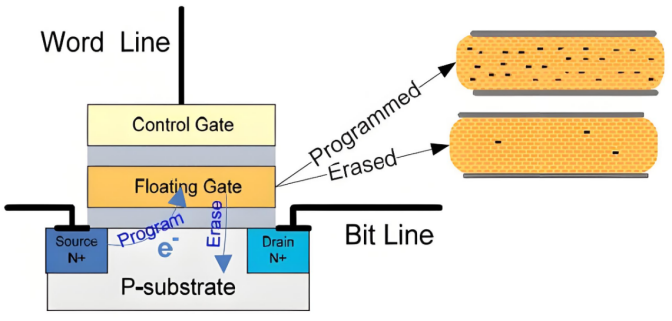

NAND Flash的基本存储单元是浮栅(Floating Gate)或电荷捕获(Charge Trap)。以传统闪存的浮栅晶体管为例,在源极(Source)和漏极(Drain)之间电流单向传导的半导体上形成存储电子的浮栅,它使用导体材料,上下被绝缘层包围,存储在浮栅极的电子不会因为掉电而消失。

存储单元操作原理:通常将浮栅极里面没有电子的状态用“1”来表示,存储一定量电子的状态用“0”表示。

写操作:在控制极施加一个大的正电压,在控制极和衬底之间建立一个强电场,使电子通过隧道氧化层进入浮栅。

擦除操作:在衬底加正电压,控制极和衬底之间建立一个反向的强电场,把电子从浮栅中“吸出来”。

读操作:在控制极施加参考电压使源极和漏极导通,确定存储单元的导通状态,从而读取出存储的信息。

存储单元结构示例图

在擦写过程中,需要在控制极与衬底之间建立强电场。随着擦写次数增加,隔离浮栅极电子的隧道氧化层效果逐渐减弱,导致电子进出浮栅极变得更容易,从而可能引发“0”、“1”翻转。因此,闪存存在擦写次数限制,通常用擦写次数(Program & Erase Cycle, PEC)来衡量闪存的寿命。读操作时施加的电压较低,不足以损伤隧道氧化层,不会影响闪存寿命。

2、NAND Flash存储模式

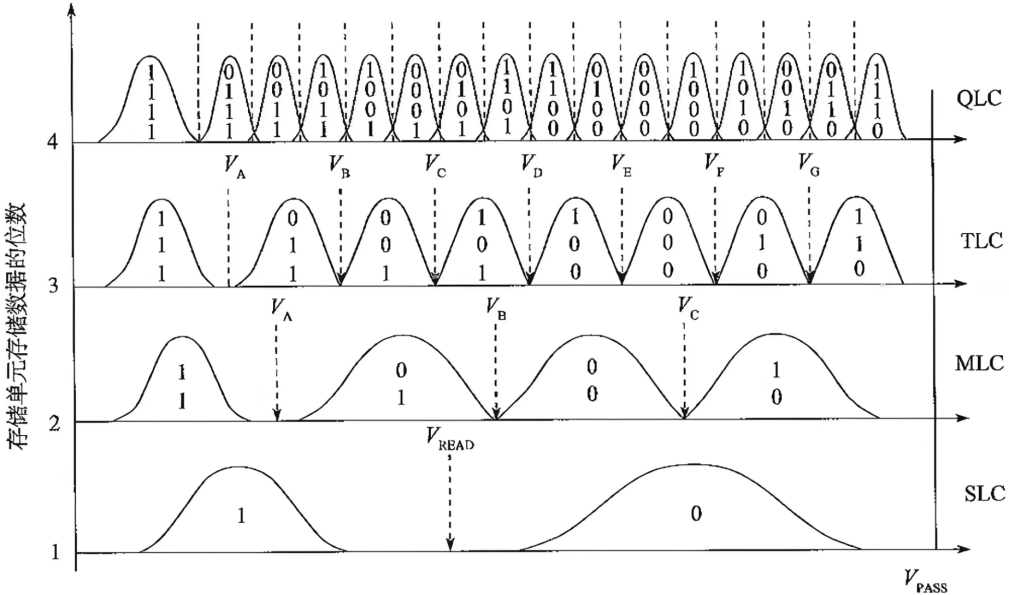

如果用一个存储单元有无电子来区分“0”和“1”,则这种每个存储单元存储1位数据的闪存称为SLC(Single Level Cell)。在通过逻辑方式提升存储密度的过程中,先后出现了SLC、MLC、TLC和QLC等类型的闪存。

具体来说,存储1位数据的闪存称为SLC,存储2位数据的称为MLC(Multiple Level Cell),存储3位数据的称为TLC(Triple Level Cell),而存储4位数据的称为QLC(Quad Level Cell)

不同类型闪存的阈值电压分布示例图

对于SLC,判断存储单元的数据是“0”还是“1”,只需在控制极施加VREAD电压;若晶体管导通则为“1”,否则为“0”。MLC、TLC和QLC的读取更复杂,需要多次读取才能确定数据,读取次数越多,所需时间越长,这是提升存储密度的代价之一。

此外,存储密度提升还会降低写入性能。每个存储单元存储的位越多,编程状态越精细,即往浮栅极注入电子的控制越精细。

随着状态增多,数据对电子流失变得更敏感,而电子流失与隧道氧化层强相关:隔绝效果越好,电子就越不容易丢失;反之亦然。虽然提高存储密度能存储更多位数据,但会带来性能下降、可靠性降低和寿命缩短等问题。

3、NAND Flash阈值电压分布图

每个存储单元对应一个阈值电压,当控制极施加的电压大于该阈值时,晶体管导通;否则,晶体管截止。通过统计某个闪存页或字线在不同阈值电压下的存储单元数量,并绘制成图,就可以得到阈值电压分布图。

以一个编程好的MLC闪存页的阈值电压分布图为例,横坐标表示阈值电压,纵坐标表示每个阈值电压对应的存储单元数量。包含不同电子数的存储单元对应不同的阈值电压,只要落在同一范围内,它们便属于同一状态。

MLC阈值电压分布示例图

为了正确读取数据,我们希望各个状态的阈值电压与读参考电压不重叠,否则会导致误判。如下图所示,若状态S2向左偏移(无色到深色),其阈值电压与读参考电压VR2部分重叠;如果仍用VR2判断是否导通,那么处于状态S2的某些存储单元可能会被误判为S1,从而导致数据读取错误。

阈值电压分布左移示例图

存储状态之间的距离越宽越好,这表示允许更多电子的意外流失或注入,从而提高闪存的容错性。然而,随着每个存储单元存储位数的增加,状态数也增多,导致各状态之间的间隔缩小,闪存的容错率降低,可靠性变差。

阈值电压分布图的绘制具有重要意义。首先,它将抽象的闪存具象化,便于具体分析与闪存相关的问题。其次,它可以帮助调试闪存故障。例如,阈值电压整体左移表明数据丢失是由于电子流失;右移则可能是意外注入电子;如果最右边的“峰”缺失,则可能是由于异常掉电。

4、闪存可靠性问题

闪存的一般可靠性问题包括磨损、读干扰、写干扰和数据保持等。

--磨损

闪存块的磨损程度通过擦写次数(PEC)衡量,其实际使用寿命与纠错算法强相关。随着擦写次数增加,浮栅极数据的可靠性降低,当出错数据超出控制器的纠错能力时,闪存将不可用。为应对磨损问题,SSD固件通常采用磨损均衡算法,使所有闪存块均摊写入,避免某些块频繁擦写,导致SSD过早出现过多坏块而失效。

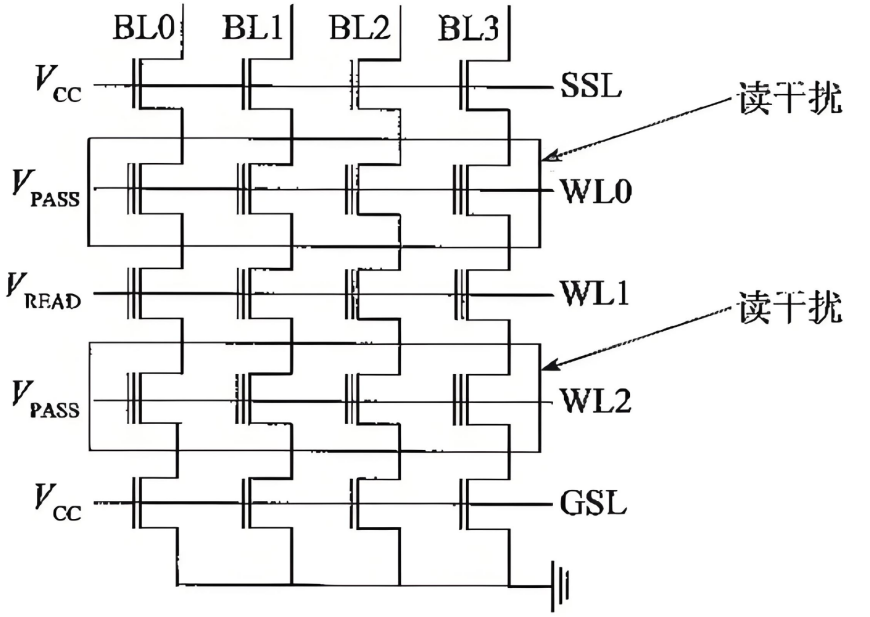

--读干扰

在读取闪存页时,为确保顺利读取目标页,需要在其他字线(Wordline,WL)上施加VPASS电压,这会导致这些WL上的晶体管发生轻微“编程”。随着读取次数增加,越来越多的电子进入浮栅晶体管,最终可能导致位翻转(由1变为0)。当翻转的位数超出纠错引擎的能力时,用户数据可能会丢失。虽然读干扰本身不会影响闪存寿命,但为解决读干扰而进行的数据刷新操作会带来额外写入,导致写放大,从而影响闪存寿命。

读干扰原理示例图

--写干扰

写干扰是指在编程某字线时,无需编程的存储单元意外地被注入电子。当在控制极施加较大电压对字线上闪存页编程时,可能导致不需要编程或已编程到位的存储单元意外注入电子,导致目标编程页写入错误数据。

--数据保持

数据存储在晶体管中,浮栅极被绝缘体包围,但随着时间推移,存储在浮栅的电子在本征电场作用下会透过绝缘体“逃逸”。尤其随着隧道氧化层隔绝效果的逐渐减弱(擦写次数增多),电子“逃逸”变得更容易。当电子逃逸达到一定量时,位“0”可能翻转为位“1”。如果位翻转数超出控制器的纠错能力,用户数据可能会丢失。数据保持期的长短不仅与擦写次数有关(擦写越多,保持期越短),还与温度有关:温度越高,数据流失越快。

NAND Flash作为核心存储技术,其基本原理和特性已被广泛认知。随着人工智能、5G、物联网等新兴技术的发展,NAND Flash面临许多可靠性挑战。然而,这些问题可以通过一些手段加以克服。存储领域的从业者正积极探索,持续更新NAND Flash的应用技术和新的可靠性解决方案。

关于云海芯科

四川云海芯科微电子科技有限公司是一家业界领先的数据存储解决方案提供商,团队核心成员深耕存储行业15+年,拥有成熟的存储产品研发上市经验。 公司扎根国产存储,坚持产品和技术创新发展,拥有闪存管理、数据保护、硬件设计等多项SSD关键技术专利,具备存储产品设计到开发的全流程交付能力,已推出NVMe和SATA全系列SSD产品,在HPC/HPDA、云计算、数据中心、虚拟化、人工智能等领域广泛应用,为金融、交通、通信、智能制造、互联网、能源等行业提供高稳定、高可靠的存储解决方案。

相关推荐